© Copyright by Steven Michael Parkes, 1994

#### A CLASS LIBRARY APPROACH TO CONCURRENT OBJECT-ORIENTED PROGRAMMING WITH APPLICATIONS TO VLSI CAD

$\mathbf{B}\mathbf{Y}$

#### STEVEN MICHAEL PARKES

B.S., University of California, Davis, 1982 M.S., University of California, Davis, 1989

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1994

Urbana, Illinois

#### A CLASS LIBRARY APPROACH TO CONCURRENT OBJECT-ORIENTED PROGRAMMING WITH APPLICATIONS TO VLSI CAD

Steven Michael Parkes, Ph.D. Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign, 1994 Prithviraj Banerjee, Advisor

Despite increasing availability, the use of parallel platforms in the solution of significant computing problems remains largely restricted to a set of well-structured, numeric applications. This is due in part to the difficulty of parallel application development, which is itself largely the result of a lack of high-level development environments applicable to the majority of extant parallel architectures. This thesis addresses the issue of facilitating the application of parallel platforms to unstructured problems through the use of objectoriented design techniques and the actor model of concurrent computation. We present a multilevel approach to expressing parallelism for unstructured applications: a high-level interface based on the actor and aggregate models of concurrent object-oriented programming, and a low-level interface which provides an object-oriented interface to system services across a wide range of diverse parallel architectures. The interfaces are manifested in the ProperCAD II library, a C++ object library supporting actor concurrency on microprocessorbased parallel architectures and appropriate for applications exhibiting medium-grain parallelism. The interface supports uniprocessors, shared memory multiprocessors, distributed memory multicomputers, and hybrid architectures comprising network-connected clusters of uni- and multiprocessors. The library currently supports workstations from Sun, shared memory multiprocessors from Sun and Encore, distributed memory multicomputers from Intel and Thinking Machines, and hybrid architectures comprising IP network-connected clusters of Sun uni- and multiprocessors. We demonstrate our approach through an examination of the parallelization process for two existing unstructured serial applications drawn from the field of VLSI computer-aided design. We compare and contrast the library-based actor approach to other methods for expressing parallelism in C++.

#### A CLASS LIBRARY APPROACH TO CONCURRENT OBJECT-ORIENTED PROGRAMMING WITH APPLICATIONS TO VLSI CAD

Steven Michael Parkes, Ph.D. Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign, 1994 Prithviraj Banerjee, Advisor

Despite increasing availability, the use of parallel platforms in the solution of significant computing problems remains largely restricted to a set of well-structured, numeric applications. This is due in part to the difficulty of parallel application development, which is itself largely the result of a lack of high-level development environments applicable to the majority of extant parallel architectures. This thesis addresses the issue of facilitating the application of parallel platforms to unstructured problems through the use of objectoriented design techniques and the actor model of concurrent computation. We present a multilevel approach to expressing parallelism for unstructured applications: a high-level interface based on the actor and aggregate models of concurrent object-oriented programming, and a low-level interface which provides an object-oriented interface to system services across a wide range of diverse parallel architectures. The interfaces are manifested in the ProperCAD II library, a C++ object library supporting actor concurrency on microprocessorbased parallel architectures and appropriate for applications exhibiting medium-grain parallelism. The interface supports uniprocessors, shared memory multiprocessors, distributed memory multicomputers, and hybrid architectures comprising network-connected clusters of uni- and multiprocessors. The library currently supports workstations from Sun, shared memory multiprocessors from Sun and Encore, distributed memory multicomputers from Intel and Thinking Machines, and hybrid architectures comprising IP network-connected clusters of Sun uni- and multiprocessors. We demonstrate our approach through an examination of the parallelization process for two existing unstructured serial applications drawn from the field of VLSI computer-aided design. We compare and contrast the library-based actor approach to other methods for expressing parallelism in C++.

# DEDICATION

To my parents, Dayle and Genie

# ACKNOWLEDGMENTS

I would like to thank my advisor, Professor Prithviraj Banerjee, for supporting and directing this work. I would like to thank the members of my committee, Professors Agha, Chien, Hwu, Patel, and Polychronopoulos, for their efforts in reviewing and critiquing my progress and this thesis.

I would like to express my thanks to the members of the ProperCAD and Paradigm projects for both their technical help in issues of parallel computing and their camaraderie. I would especially like to thank John Chandy, my officemate, who not only served as a source of insight and a sounding board for ideas but also developed several large applications on the ProperCAD II library with virtually no documentation.

I would like to thank the members, both present and former, of the Center for Reliable and High Performance Computing. Special thanks are due to Ken Kubiak for technical insight, encouragement, and empathy.

I owe a great debt to my parents, Dayle and Genie, and my siblings, Cheryl, Chris, and Debbie, for their invaluable love, encouragement, and understanding during my doctoral degree program.

This work was supported in part by the Semiconductor Research Foundation. The Argonne National Laboratory, the San Diego Supercomputer Center, and the National Center for Supercomputer Applications provided support by providing access to their computing resources.

# TABLE OF CONTENTS

| Chapter |                                        |                                                            | Page |  |

|---------|----------------------------------------|------------------------------------------------------------|------|--|

| 1       | INT                                    | RODUCTION                                                  | . 1  |  |

|         | 1.1                                    | Computer-Aided Design for VLSI                             |      |  |

|         | 1.2                                    | A Class Library for Concurrent Object-Oriented Programming |      |  |

|         | 1.3                                    | Summary of Contributions                                   |      |  |

|         | 1.4                                    | Overview                                                   |      |  |

| 2       | CONCURRENT OBJECT-ORIENTED PROGRAMMING |                                                            |      |  |

|         | 2.1                                    | Hardware Architectures                                     | . 9  |  |

|         | 2.2                                    | High-level Programming Models                              | . 11 |  |

|         | 2.3                                    | Implementation Architectures                               |      |  |

|         | 2.4                                    | Composability                                              |      |  |

|         | 2.5                                    | A Class Library Approach                                   |      |  |

|         | 2.6                                    | Other Models and Implementations                           |      |  |

| 3       | THE ACTOR INTERFACE                    |                                                            |      |  |

|         | 3.1                                    | Actors and Continuation Passing Style                      | . 30 |  |

|         | 3.2                                    | Concurrent Objects                                         |      |  |

|         | 3.3                                    | Concurrent Collections                                     |      |  |

|         | 3.4                                    | Performance                                                |      |  |

|         | 3.5                                    | Evaluation                                                 | . 47 |  |

|         | 3.6                                    | Other Actor Models and Implementations                     | . 51 |  |

| 4       | ABS                                    | STRACT PARALLEL ARCHITECTURE                               | . 56 |  |

|         | 4.1                                    | Thread Management                                          | . 56 |  |

|         | 4.2                                    | Resource Management                                        | . 64 |  |

|         | 4.3                                    | Communication Management                                   |      |  |

|         | 4.4                                    | Configuration Management                                   |      |  |

|         | 4.5                                    | Performance                                                |      |  |

|         | 4.6                                    | Evaluation                                                 |      |  |

|         | 4.7                                    | Other Models and Implementations                           |      |  |

| 5 | ME                        | FA-PROGRAMMABILITY                                |  |  |  |

|---|---------------------------|---------------------------------------------------|--|--|--|

|   | 5.1                       | Local Meta-programmability                        |  |  |  |

|   | 5.2                       | Global Meta-programmability                       |  |  |  |

|   | 5.3                       | Evaluation                                        |  |  |  |

|   | 5.4                       | Other Models and Implementations                  |  |  |  |

| 6 | PARALLEL TEST GENERATION  |                                                   |  |  |  |

|   | 6.1                       | Test Pattern Generation                           |  |  |  |

|   | 6.2                       | HITEC: A Serial Test Generator                    |  |  |  |

|   | 6.3                       | Approaches to Parallel Test Generation            |  |  |  |

|   | 6.4                       | Parallel Test Generation using Actor Parallelism  |  |  |  |

|   | 6.5                       | ProperHITEC                                       |  |  |  |

|   | 6.6                       | Performance                                       |  |  |  |

|   | 6.7                       | Evaluation                                        |  |  |  |

| 7 | PARALLEL FAULT SIMULATION |                                                   |  |  |  |

|   | 7.1                       | Fault Simulation                                  |  |  |  |

|   | 7.2                       | PROOFS: A Serial Fault Simulator                  |  |  |  |

|   | 7.3                       | Approaches to Parallel Fault Simulation           |  |  |  |

|   | 7.4                       | Parallel Fault Simulation Using Actor Parallelism |  |  |  |

|   | 7.5                       | ProperPROOFS                                      |  |  |  |

|   | 7.6                       | Performance                                       |  |  |  |

|   | 7.7                       | Evaluation                                        |  |  |  |

| 8 | CONCLUSIONS               |                                                   |  |  |  |

|   | REF                       | <b>ERENCES</b>                                    |  |  |  |

|   | VIT                       | A                                                 |  |  |  |

vii

# LIST OF TABLES

| TableI |                                                                    | Page |

|--------|--------------------------------------------------------------------|------|

| 3.1    | Costs of actor primitives                                          | 45   |

| 4.1    | Round-trip latency for IP message passing                          | 77   |

| 4.2    | Bandwidth for IP message passing                                   |      |

| 4.3    | APA triples for various machines                                   |      |

| 4.4    | Lines of code in APA                                               | 79   |

| 6.1    | Classes in HITEC                                                   |      |

| 6.2    | ProperHITEC results on Sun 4/670MP                                 |      |

| 6.3    | ProperHITEC results on Intel iPSC/860                              |      |

| 6.4    | ProperHITEC results on Encore Multimax                             |      |

| 6.5    | ProperHITEC results on clusters                                    |      |

| 6.6    | Increased efficiency in ProperHITEC                                |      |

| 6.7    | Comparison of ProperHITEC and ProperTEST on iPSC/860               |      |

| 6.8    | Comparison of software metrics for HITEC and ProperHITEC           |      |

| 6.9    | ActorMethods for each class in ProperHITEC                         | 120  |

| 6.10   | Member functions in HITEC and ProperHITEC                          |      |

| 6.11   | New virtual members in HITEC                                       | 121  |

| 7.1    | Run time and speedup for static fault distribution on the iPSC/860 | 130  |

| 7.2    | Time (ms) of fault simulation operations                           |      |

| 7.3    | ProperPROOFS results on Intel iPSC/860: random vectors             | 137  |

| 7.4    | ProperPROOFS results on Intel Paragon: random vectors              |      |

| 7.5    | ProperPROOFS results on Sun 4/670MP: random vectors                | 139  |

| 7.6    | ProperPROOFS results on Intel iPSC/860: STG vectors                |      |

| 7.7    | ProperPROOFS results on Intel Paragon: STG vectors                 | 141  |

| 7.8    | ProperPROOFS results on Sun 4/670MP: STG vectors                   |      |

| 7.9    | Good and faulty simulation of s35932 on Paragon                    | 143  |

| 7.10   | Comparison of static and dynamic fault distribution on iPSC/860    | 144  |

| 7.11   | Comparison of software metrics for PROOFS and ProperPROOFS         |      |

|        | ActorMethods for each class in ProperPROOFS                        |      |

| 7.13   | Member functions in PROOFS and ProperPROOFS                        | 147  |

# **LIST OF FIGURES**

-

| Figure |                                                   |       |

|--------|---------------------------------------------------|-------|

| 1.1    | An overview of the ProperCAD project              | . 5   |

| 2.1    | Shared memory multiprocessor                      | . 10  |

| 2.2    | Distributed memory multiprocessor                 | . 10  |

| 2.3    | Hybrid multiprocessor                             | . 12  |

| 2.4    | Communication and consistency in shared memory    | . 13  |

| 2.5    | Communication on distributed memory architectures | . 14  |

| 2.6    | Spectrum of parallelism                           | . 20  |

| 2.7    | Composability in send-receive and actor models    | . 23  |

| 3.1    | Actor operations                                  | . 31  |

| 3.2    | RPC and Actors/CPS                                |       |

| 3.3    | Implementations of a concurrent array             | . 41  |

| 4.1    | APA thread management classes                     | . 57  |

| 4.2    | Use of ThreadManager class                        | . 63  |

| 4.3    | APA free store management classes                 | . 65  |

| 4.4    | Reservoir size mapping                            | . 68  |

| 4.5    | Datagram layout                                   | . 69  |

| 4.6    | APA dimensions                                    | . 81  |

| 5.1    | Task queues                                       | . 87  |

| 5.2    | Priority class hierarchy for ATPG                 | . 88  |

| 5.3    | Heterogeneous lexicographic priorities            |       |

| 5.4    | Call by value and first class values              | . 91  |

| 6.1    | HITEC/PROOFS organization                         | . 106 |

| 6.2    | Parallelism in ProperHITEC                        | . 110 |

| 6.3    | ProperHITEC organization                          | . 113 |

| 7.1    | Fault simulation table model                      | . 123 |

| 7.2    | Concurrent and deductive fault simulation         | . 124 |

| 7.3    | Differential fault simulation                     | . 124 |

| 7.4    | Bit-parallel fault simulation                     | . 125 |

| 7.5 | PROOFS organization                   | 127 |

|-----|---------------------------------------|-----|

| 7.6 | Split request in fault redistribution | 131 |

| 7.7 | Forwarding of split requests          | 133 |

| 7.8 | ProperPROOFS organization             | 134 |

# LIST OF INTERFACES

## Interface

# Page

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | class<br>class<br>class<br>class | Actor       33         ActorName       35         Continuation       37         Continuation       40         Aggregate       42         AggregateName       43 |

|----------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1                                    | class                            | Thread                                                                                                                                                          |

| 4.2                                    | class                            | Process                                                                                                                                                         |

| 4.3                                    | class                            | ProcessGroup                                                                                                                                                    |

| 4.4                                    | class                            | Cluster 61                                                                                                                                                      |

| 4.5                                    | class                            | ThreadManager 62                                                                                                                                                |

| 4.6                                    | class                            | FreeStore                                                                                                                                                       |

| 4.7                                    |                                  | PageTable 66                                                                                                                                                    |

| 4.8                                    |                                  | Reservoir                                                                                                                                                       |

| 4.9                                    | class                            | Datagram                                                                                                                                                        |

|                                        |                                  | Semaphore                                                                                                                                                       |

| 4.11                                   | class                            | Machine                                                                                                                                                         |

| 4.12                                   | class                            | Network 74                                                                                                                                                      |

| 5.1                                    | class                            | TaskQueue                                                                                                                                                       |

| 5.2                                    | class                            | Priority                                                                                                                                                        |

| 5.3                                    | class                            | PriorityComparator                                                                                                                                              |

| 5.4                                    | class                            | Value                                                                                                                                                           |

| 5.5                                    |                                  | Distribution                                                                                                                                                    |

| 5.6                                    | class                            | Director                                                                                                                                                        |

# Chapter 1 INTRODUCTION

The desire to utilize multiple processors to solve significant computing problems has, to date, been largely unattainable for all but a set of restricted problems, namely the numerical problems found in scientific applications and the database problems found in transaction-processing applications. While substantial computing problems exist in other fields, the techniques and implementations used in the parallelization of scientific and transaction-processing applications have not proven similarly effective on unstructured problems. The lack of structure in these classes of problems de-emphasizes floating point vector operations while it emphasizes operations that comprise a mixture of integer and floating point instructions on pointer-based data structures. Existing parallelization methods, both manual and automatic, often fail on this class of application to achieve results comparable to those on numeric and structured applications.

With increasing interest in the parallelization of a larger set of applications comes a shift in the way in which parallelization is approached. For example, many classical parallel applications have been developed to solve specific research problems; these efforts were often targeted toward specific architectures—those available to the researchers. Because the result of the research was the knowledge gained by solving a particular problem and not a parallel application, the dependence on a particular architecture was not considered a significant drawback.

In contrast, as parallel machines have proliferated, a broader range of application designers has been attracted. For these designers, the lack of a dominant architecture or particular machine engenders the need to pursue an architecture-independent solution to archive a cost-effective solution. Moreover, a significant degree of new interest in scalable platforms is coming from vendors of existing serial applications. As a result, there is need for parallelization methods that can be incrementally applied to existing code. Finally, because the

cost of developing parallel software is inherently greater than that of developing serial software, the recent interest in code reuse is at least as strong in parallel processing as it is in serial processing.

Technologies from concurrent object-oriented programming can be used to address each of these issues. Abstract high-level models can be used to provide a degree of insulation from architectural details. Encapsulation via well-defined interfaces can be used to facilitate modular development and code reuse. Inheritance and dynamic binding can be used to facilitate incremental parallelization of existing serial object-oriented applications.

While these technologies exist in the field of concurrent object-oriented programming, they take numerous diverse forms. Generating a cohesive interface that meets all application needs is probably infeasible; not only do the requirements of different fields vary widely, the evaluation of a 'good' interface often varies among individuals, even within the same field.

In this work, we present an interface for concurrent object-oriented programming that is applicable to computer-aided design (CAD) applications for VLSI. To the extent that VLSI CAD applications are characteristic of large C<sup>++</sup> applications, the interface should also find application in other domains. The interface is defined in terms of C<sup>++</sup> classes and implemented in the ProperCAD II class library. In the remainder of this chapter, we consider the characteristics of VLSI CAD applications, briefly comment on how a class library can be used to parallelize CAD applications, summarize the contributions of this research, and give an overview of the chapters that follow.

# 1.1 Computer-Aided Design for VLSI

To design increasingly complex VLSI systems, continued—and in some cases radical progress is required in design technologies, especially the algorithms and applications for VLSI CAD. CAD applications differ substantially from the scientific applications which have traditionally formed the bulk of supercomputing workloads. CAD applications are characterized by:

- long execution times, sometimes more than a week for individual runs on contemporary uniprocessor platforms

- qualities of result which are directly dependent on the magnitude of computing resources applied

- a direct correlation between application turnaround time and design cycle length

- multimegabyte data sets

- irregular, unstructured data organizations

- resistance to well-known parallelization techniques

Examples of VLSI CAD problems are test pattern generation, logic synthesis, circuit extraction, and cell placement and routing.

Automatic test pattern generation (ATPG) for VLSI circuits is the process of generating *test patterns*, sets of inputs to integrated circuits that are applied to fabricated devices to determine if any defects occurred during manufacturing. Although the complexity of ATPG is daunting—it is an NP-complete search problem—it is nonetheless considered indispensable for maintaining the manufacturing quality of ever larger VLSI devices.

Logic synthesis comprises the creation and optimization of digital circuits represented as netlists of logic and state elements. Because of increasing circuit densities, the last decade has seen a considerable increase in interest in algorithms for the automatic synthesis of VLSI circuits. There is industry consensus that only through synthesis will it be possible to manage the design complexity of the current and future generations of VLSI chips. Most synthesis algorithms are both memory and processor intensive and display a quality of results tightly coupled to the resources applied.

Circuit extraction is the process of taking a VLSI mask-level layout and extracting circuit connectivity and parametric values. The results of extraction are used to verify both design correctness and performance requirements, usually after automatic placement and routing. Extraction is typically performed on a circuit description provided in terms of rectangles on various mask layers. The number of rectangles is approaching 100 million in contemporary microprocessor designs; few platforms available in industry have the resources to handle these designs efficiently. Given the frequency of use—extraction is iterated with design changes to verify changes and to update extracted parametric information—techniques to take advantage of all available resources are invaluable.

When the logic design for a VLSI circuit has been completed, cell placement and routing are performed. With chips approaching tens of millions of gates, the time required for this process on large chips often exceeds days and is quickly approaching weeks on state-of-theart workstations. As in other CAD tasks, the quantity of resources applied to the problem has a direct impact on the quality of results.

Even with the preponderance of evidence indicating that virtually any method of managing the application development process and any technique for improving quality through additional resources would appear promising, it is still the case that neither parallel processing nor object-oriented techniques are well represented in the CAD development community. This situation is not without justification for a number of reasons:

- For more than a decade, most CAD development has been performed in the C programming language, and until the advent of C<sup>++</sup>, use of an object-oriented language implied the sacrifice of existing code, an unacceptable alternative. Even with the availability of C<sup>++</sup>, adoption is slow; C<sup>++</sup> is significantly more complicated than C and is still undergoing rapid development. Development tools are only now attaining the degree of stability required for even the most aggressive commercial development.

- Due to a lack of widely available libraries, much of the promise of code reuse associated with object-oriented programming remains to be realized. Given the ability in C++ to trade flexibility for efficiency, the process of generating reusable code is complicated by the fact that the set of design choices, in terms of flexibility versus overhead, for one application may not be acceptable for another; CAD problems, with their inherent complexity and size, are known to be sensitive to overheads in area or space.

- Until recently, the widespread availability to CAD users of parallel platforms has been severely limited. Supercomputers have in general been limited to the restricted application domains mentioned previously. The techniques developed for these platforms have had no place for application in the CAD community. With little availability of parallel platforms, interest in parallel solutions to CAD problems has been relatively low. With only limited development of parallel applications, little impetus exists for CAD users to explore the cost benefit trade-off of parallel platforms.

- The generation of efficient parallel algorithms has been impeded by concurrent rapid improvements in serial algorithms. Often by the time a parallel CAD algorithm is completed, it lags significantly behind the quality, and sometimes even the performance, of contemporary serial algorithms. Given the high cost of developing new applications, support for a parallel track of separate parallel tools which mirrors a set of serial tools is prohibitive.

Figure 1.1 An overview of the ProperCAD project

actor model of concurrent object-oriented programming with a statically typed imperative language, C<sup>++</sup>, and a low-level abstract machine interface that can be used to parametrically describe a wide variety of concrete architectures.

The development of the interface has been driven by and evaluated against two new parallel applications, parallel test pattern generation and parallel fault simulation, each incrementally developed from an existing state-of-the-art serial application. In addition to providing a basis for evaluating the usability of the interface, these applications embody new approaches to their target problems.

# 1.3 Summary of Contributions

The primary contributions of this thesis are:

- 1. A class library interface for actor-based parallelism in a statically typed language and based on built-in type mechanisms.

- 2. An implementation of aggregates providing the functionality described in [5] with additional meta-programmability features.

- 3. An interface supporting composable meta-programming of an actor system on contemporary microprocessor-based machines.

- 4. An open implementation supporting application-specific customization of the run time support system.

- 5. An abstract parallel architectural model with a class library interface, capable of parametrically describing the majority of contemporary parallel architectures.

- 6. New parallel algorithms for test pattern generation and fault simulation incrementally derived from state-of-the-art serial algorithms.

# 1.4 Overview

In Chapter 2, we review recent work in the field of concurrent object-oriented programming and consider application of object-oriented programming techniques to unstructured problems. Chapter 3 presents the primitives in the actor interface. In Chapter 4, we consider a platform for implementation of the actor primitives, the abstract parallel architecture. Chapter 5 presents extensions of the actor interface to support for meta-programmability. Chapter 6 introduces test generation, an unstructured application drawn from the area of VLSI CAD, and demonstrates how the interfaces developed in this work are used to parallelize an existing serial test application. Chapter 7 presents the parallelization of fault simulation by using the actor and aggregate models and reports an implementation based on the ProperCAD II library. Chapter 8 summarizes our experiences parallelizing serial applications using the new interface, presents observations on the most significant success of the interface, and proposes features that would extend the usability of the interface and implementation.

# Chapter 2 CONCURRENT OBJECT-ORIENTED PROGRAMMING

Concurrent computing is the use of multiple processors to solve a single problem. Concurrent machines have existed almost as long as computers themselves, yet the use of concurrency to improve run times and results is still limited to a few specialized areas. This is in large part due to the difficulty in producing concurrent programs that are both effective in improving performance and manageable from a development perspective.

When creating concurrent programs, the programmer must deal with two competing issues: expression of concurrency and control of the state interference caused by concurrency. Expression of concurrency is the task of breaking a problem into multiple subproblems that can be then processed concurrently. In this respect, a serial program is the degenerate case of a concurrent program. If insufficient concurrency is expressed in a program, the effectiveness of the program will be limited. A program with limited concurrency is not scalable, i.e., there is a bound on the number of processors which can be applied to the problem beyond which processor utilization falls dramatically. While limits in scalability argue for highly concurrent programs, programs of this type have drawbacks as well. First, if a highly concurrent program has a low ratio of computation to communication, it may fail to achieve sufficient processor utilization. Second, when additional concurrency is expressed, the issue of state interference arises. If two concurrent tasks reference data whose values change as computation progresses, the likelihood of race conditions due to intertask interference rises. Thus, when a programmer expresses additional concurrency, he must at the same time ensure that state interference does not invalidate the result of the program.

In concurrent object-oriented programming [6], the object model and object-oriented programming primitives are used to address issues of expression of concurrency and man-

agement of interference. In this chapter, we broadly review hardware architectures, programming models, and programming model implementations. We conclude the chapter with a broad overview of the library interface developed in this work and presented in greater detail in following chapters.

## 2.1 Hardware Architectures

Parallel architectures cover a broad range of implementations, from low concurrency systems composed of as few as two processors to highly-concurrent systems with thousands of processors. Concurrent architectures also vary in both the manner and efficiency of communication, from systems with interprocessor bandwidths of hundreds of megabytes per second and communication frequency on the order of a few instructions to systems with a few megabytes per second bandwidth and communication latencies in milliseconds.

Traditionally, concurrent architectures could be cleanly divided into two classes, *shared memory* architectures and *distributed memory* architectures. In recent years, *distributed shared memory* (logically shared, physically distributed) architectures such as the Kendall Square KSR-1 [7] have been introduced. Additionally, with the rapid increase in interconnectivity via local- and wide-area networks, virtually all machines can now be considered concurrent in as much as they support some form of message passing interconnection.

This section considers a few key characteristics of each of these architecture classes. It should be noted that these are *hardware* architectures and do not necessarily reflect the programming model as viewed by the application programmer. It is possible, via compilers, run time libraries, and operating systems, to implement any of the application programming models of the next section on any of the hardware architectures presented below. We use the term *low-level programming model* to describe the model supported directly by the hardware and *high-level programming model* to describe the model seen by applications. High-level programming models are considered in Section 2.2.

#### 2.1.1 Shared memory

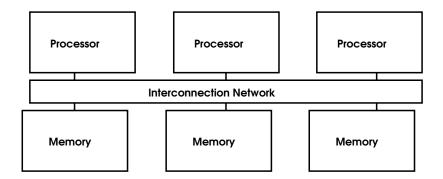

Shared memory architectures are constructed from a number of processing and memory modules which are connected via an interconnection network (Figure 2.1). In the first generation of shared memory machines, processing modules generally lacked memory other than that represented by the registers in each CPU and the interconnection network was generally a bus. Both of these characteristics led to scaling problems. To improve performance,

Figure 2.1 Shared memory multiprocessor

local caches were added to each processor. While this addition drastically cuts the latency of memory references it introduces problems of cache coherency. More advanced interconnection networks have also been developed, including crossbar and multistage networks. Even though the addition of cache mechanisms has enabled the scaling of shared memory machines to larger sizes, the difficulty of maintaining cache coherence typically limits the feasibility of this approach to tens of processors. It is the cache coherence of these models that distinguishes them from other uniform address space models.

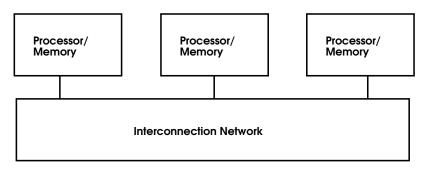

#### 2.1.2 Distributed memory

In distributed memory architectures, each processing module consists of both a processor and local memory. Processor modules are interconnected by a network (Figure 2.2). The most significant characteristics of distributed memory systems are the individual address space of each processor and explicit access to the network via primitives such as send and receive. The bandwidth of the network in these architectures has traditionally been less than that of shared memory machines—often an order of magnitude less than those of bus-based shared memory machines—and often varies among different pairs of processors. However, as a result, these architectures are considered more scalable than shared memory

Figure 2.2 Distributed memory multiprocessor

ory architectures. Machines of this type have been built with thousands of processors. The lower bandwidth of the network means that algorithms that perform well on shared memory machines may perform poorly on distributed memory architectures, if a naïve mapping of shared memory reference to distributed memory communication primitive is used.

#### 2.1.3 Distributed shared memory

In the last decade, a new architecture has been developed using techniques borrowed from both the pure shared memory and pure distributed memory architectures. This architecture uses hardware components similar to those developed for purely distributed memory to implement a low-level programming model that mirrors shared memory. Though an interconnection network is used, the hardware does not support explicit send and receive primitives. Instead, the low-level programming model is a uniform address space, and the hardware detects accesses to nonlocal memory, sending the appropriate messages to gain access to the necessary data. Consistency in these systems is usually maintained via a combination of hardware and software in a mechanism called a directory [8]. Contemporary machines in this class are nonuniform memory architecture (NUMA) machines such as the Stanford DASH [8] and cache-only memory architecture (COMA) machines such as the KSR-1 [7].

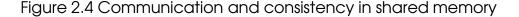

### 2.1.4 Hybrid shared and distributed memory

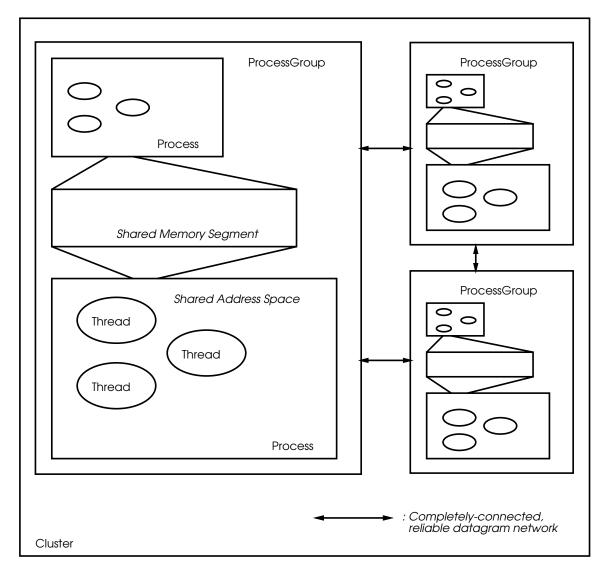

Hybrid architectures combine shared and distributed memory architectures without adopting a completely shared or distributed model. Some processors will share a uniform address space; otherwise, communication requires explicit sends and receives (Figure 2.3). With the recent concurrent growth in workstation clusters and desktop multiprocessors, hybrid machines are becoming ubiquitous. Furthermore, massively parallel processor (MPP) manufactures are beginning to consider hybrid architectures for their machines; the Intel Paragon supports configurations which have shared memory multiprocessors at each node within the mesh interconnect [9].

# 2.2 High-level Programming Models

In this context, "high-level" indicates the programming model to which an application is written; this may differ from the model used by the underlying operating system. The programming model can be broken into two components, a *communication model* and a *thread*

Figure 2.3 Hybrid multiprocessor

*model.* Though a complete model requires aspects of both components, separate consideration of the components helps clarify the issues while illustrating the space of complete models. While only a few combinations are currently in use, almost any combination of communication and thread models can form a new complete programming model. These models are high-level and thus with proper software support could be implemented on any of the hardware architectures described in the previous section, albeit possibly at higher cost if the programming and hardware models are dissimilar.

## 2.2.1 Communication model

The communication model defines how the "threads" of a program coordinate data interchange amongst themselves. Though we use the term 'thread' in this section, we defer definition to Subsection 2.2.2. For the purposes of this subsection, threads may be considered an active execution environment (stack) that vies for processor time with other threads.

#### 2.2.1.1 Shared memory

In the shared memory programming model, the application sees a single flat address space. Communication is implicit, through access to shared variables. To fully support such a model, a method of interprocessor synchronization is necessary, usually implemented at the lowest level via atomic operations such as test-and-set or through higher-level abstractions such as barriers. The exact semantics of synchronization, i.e., busy-wait versus rescheduling, cannot be defined precisely without reference to a thread model.

Specifying the exact semantics of shared memory machines is complicated by the existence of different *consistency models*. With hardware support for caching and load/store reordering, the most conservative model of shared data consistency, *sequential consistency* [10], is prohibitively expensive. Thus, in addition to the uniform address space, a shared memory model must explicitly define the aspects, both deterministic and nondeterministic, of access to shared memory.

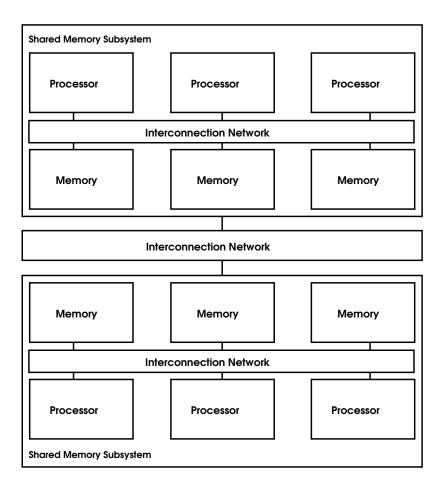

An example of shared memory communication is shown in Figure 2.4. In the figure, two threads access two shared integer variables, a and b. Because the model specifies a uniform address space, the variables exist at the same addresses in both threads. The figure demonstrates the consistency problem. While the first thread stores five into a followed by storing ten into b, it is possible, under existing consistency models, for the second thread to see the change to b before seeing the change to a.

Before: a = 1; b = 2; c = 3; d = 4; Thread 1 Thread 2 a = 5; c = b; b = 10; d = a; b = 10; d = a; c = b; b = 10; c = 10; d = 5; a = 5; b = 10; c = 10; d = 5; a = 5; b = 10; c = 2; d = 1;

#### 2.2.1.2 Distributed memory

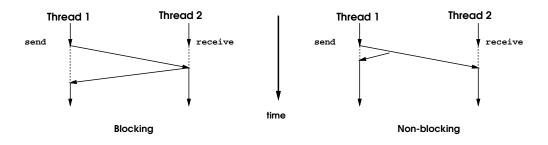

In the distributed memory model, a send primitive is used to send data from one thread to another thread. An explicit receive operation must be executed before the data is available to the receiving thread. Figure 2.5 shows two possible ways communication can occur in a distributed memory model. In the blocking case, the send operation does not complete until the corresponding receive operation has begun. This style of communication is one of the types supported by the Thinking Machines CM-5 CMMD library [11]. In the nonblocking case, the send operation completes when the necessary data are copied out of the application buffer; it is not necessary that the corresponding receive be executed. This type of communication is common on Intel multicomputers [12]. Variations on communications primitives provide for broadcasting, multicasting, synchronous and asynchronous communication, and typed messages.

#### 2.2.2 Thread models

There are two principal thread models, physical and virtual.

#### 2.2.2.1 Physical threads

In a physical thread model, the thread, as seen by the application, is a processing element and is generally available for "exclusive" use by the application; if the code running on a thread executes a blocking call, the entire thread is blocked for the duration of the call. The physical model includes those systems which provide more threads than processors but for which the application cannot rely on the ability of the underlying run time library to efficiently handle a number of threads vastly greater than the number of available processors.

Figure 2.5 Communication on distributed memory architectures

#### 2.2.2.2 Virtual threads

In a virtual thread model, the number of threads visible to the program is typically not related to the number of processing elements. Applications developers think in terms of a number of threads convenient for the application at hand. It is the responsibility of the underlying language and run time support to map these virtual threads to physical processors. When a virtual thread blocks, it is expected that the underlying run time support will find another virtual thread to schedule. This model is often referred to as *light-weight threads*.

#### 2.2.3 Complete models

A complete model is created by combining a communication model with a thread model and then specifying the semantics of the interaction between the two components. We consider three complete high-level models; many more are possible, but the examples serve to demonstrate the issues involved.

#### 2.2.3.1 Unix shared memory multiprocessor

The model generally found on Unix shared memory machines combines shared memory communication and physical thread components. The underlying consistency model is that of the underlying hardware and varies from architecture to architecture. The model is considered physically threaded, because Unix operating systems—in particular, the scheduler—typically do not perform well when the number of kernel-scheduled threads is far greater than the number of processors, e.g., 100 times or more.

#### 2.2.3.2 MPI

The Message Passing Interface (MPI) is a send-receive model recently standardized by a consortium of manufactures and users [13]. The model is similar to the programming interfaces on the Intel iPSC and Paragon multicomputers and those supplied by libraries such as PVM [14] and Express [15].

The basic model provides a send-receive interface atop a physically threaded model. Programs written for this model are written for a fixed number of processors. While they can be parameterized by the size of the machine, the model provides little or no support for context switching of a physical thread over multiple virtual threads. In MPI, the basic send-receive model is augmented with such concepts as process groups and environments, which makes the interface more applicable to virtual threads. Experience with this advanced virtual thread interface on distributed memory systems is limited.

#### 2.2.3.3 Actors

The actor model is based on continuation passing [16] using virtual threads. From the application viewpoint, an actor is an object with its own thread of control that at most times is blocked waiting for a message—a continuation execution of one of its methods.

Continuation passing resembles message passing but omits the explicit receive operation. Instead, each message sent contains enough information to determine the action to be invoked by the receiver. In this way, the model is similar to *active messages* [17].

The actor model combines continuation passing with a virtual thread model. Most of the time, the thread associated with an actor is blocked awaiting the continuation execution of one of its methods. When a continuation destined for the actor is executed, the appropriate member function is executed. As part of the execution, the actor may execute other continuations, create new actors, or perform computations, possibly with side effects.

In a parallel context, continuations express parallelism; the call to a continuation returns after scheduling the future execution of the continuation body rather than synchronizing with the actual execution. Since every actor has a thread and an actor is simply a concurrent object, actor programs typically have thousands, if not hundreds of thousands, of virtual threads. Thus, the virtual thread mechanism used by an actor implementation must be efficient.

As the actor model is the model adopted in this work, further discussion and examples are deferred until discussion of the Actor Interface in Chapter 3.

# 2.3 Implementation Architectures

Many of the choices made in the development of the characteristics of the interface in this work involved consideration of what developers of the applications in the targeted fields would need and like. A study of these issues is presented by Pancake et al. [18], [19]; while their work was centered on scientific problems, with a few exceptions their observations and conclusions are equally applicable to other problem domains. We borrow from their discussion, as we consider the characteristics desirable in VLSI CAD and similar domains.

## 2.3.1 Algorithm classifications

#### 2.3.1.1 Regular versus irregular

Regular applications are those whose computation demonstrates a regular pattern, i.e., the iteration of a large number of operations on large contiguous regions of memory with little change in control flow or memory access patterns. Examples are signal processing applications which compute fast Fourier transforms and other transforms on dense arrays of raw data.

In contrast, irregular problems do not deal with dense contiguous data structures. This class includes not only algorithms defined on completely arbitrary data structures but also algorithms which have a high degree of conceptual regularity but a low degree of regularity in implementation. Among this later class are sparse matrix operations; while the multiplication of two sparse matrices is at a high level a regular operation, in terms of low-level operations, control and data access patterns differ significantly from that of the analogous dense operation. Typically, the metric used to differentiate regular from irregular is the applicability of vector operations.

#### 2.3.1.2 Structured versus unstructured

For our purposes, we define unstructured problems as those that are not naturally expressible as operations on (possibly sparse) vectors and matrices or through iterative solution of a number of conceptually identical problems. Thus, while a sparse matrix operation is not a regular operation, it is highly structured; the operation can be succinctly described as a simple iteration over two graphs.

In contrast, unstructured problems are those for which a number of heterogeneous tasks must be performed. For example, in a CAD application, it may be necessary to concurrently process cost estimation tasks, database update tasks, and global status coherence tasks. The number of unstructured problems implemented only on uniprocessor is large; the area of CAD for VLSI circuits is dominated by such applications.

#### 2.3.1.3 Numeric versus non-numeric

Traditionally concurrent processing has been applied to predominately numeric applications. For example, physical modeling tasks are well represented in current parallel processing applications. These applications tend to be dominated by floating point operations on data representing physical quantities. While there are a number of problems involving physical modeling in the domain of VLSI CAD, the area is dominated by applications for which floating point operations do not predominate. These applications, such as logic synthesis, test generation, and logic simulation, are tightly tied to the logic model of digital circuits and tend to be dominated by integer and logic instructions.

#### 2.3.1.4 Fine-grain versus medium-grain versus coarse-grain

The granularity of a parallel algorithm refers to the relative ratio of computation to commutation. A fine-grain application expresses far more concurrency and utilizes far more communication than a medium-grain application. It is difficult to affix a label to any particular algorithm, since these terms are largely relative. We choose to describe our approach as applicable to medium-grain concurrency and to describe the most useful distinctions between fine- and coarse-grain without reference to instruction counts.

Fine-grain applications are those for which virtually every operation is concurrent. This concurrency may be implied by data distribution as in a data parallel context or by implicit concurrency in all operations as in the actor model.

We consider coarse-grain parallel algorithms to be those which either limit the number of effectively processed concurrent tasks to the number of physical processors in the machine or for which the communications protocol implies crossing a protection boundary. Thus, an algorithm that is coarse-grained generally is written explicitly in terms of the size of the machine, i.e., it is physically threaded, or expects intervention in communication as is the case for distributed processing via remote procedure calls (RPCs) [20].

Essentially, applications which do not fit either of the previous two categories may be considered medium-grain, and thus many systems can be considered medium grain. The predominant characteristics of medium grain would then be:

- existence of a mixture of concurrent and nonconcurrent objects with concern for efficiency as the number of concurrent objects grows.

- an assumption of efficiency in communication, i.e., when possible, communication among concurrent tasks should be on the order of a function call in a serial language.

#### 2.3.2 Interface levels

#### 2.3.2.1 Low-level

A low-level model essentially reflects the underlying hardware with little or no abstraction. Such a model is clearly not architecture-independent.

#### 2.3.2.2 High-level

A high-level model provides a degree of distance or abstraction from the underlying hardware. A high-level model should be implementable across a range of architectures, although with varying degrees of efficiency. While high-level models are conceptually very attractive, they may suffer from greater overheads and may inhibit some kinds of optimizations.

#### 2.3.2.3 Mixed-level

Because high-level interfaces either incur too much overhead or because a degree of architectural tuning is required, many have been been augmented with low-level features, which leads to a mixed-level interface. While mitigating the disadvantages of a purely high-level model, a mixed model can become difficult to understand and manage [18].

#### 2.3.2.4 Multiple levels

Rather than mixing high- and low-level features, two models can be provided, one high and one low, with a well-defined interface. This combination of models should provide greater flexibility than a purely high-level model while helping minimize the confusion resulting from a single interface with arbitrarily mixed abstractions.

#### 2.3.3 Expression of parallelism

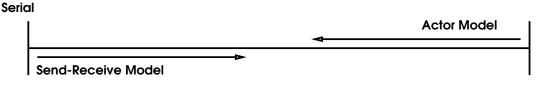

One can view the gamut of parallelism as a one-dimensional space with extremes representing completely serial and completely parallel programs. This situation is portrayed graphically in Figure 2.6, where arrows indicate increasing programmer effort.

If we consider, for example, the MPI and actor programming styles, we see that they lie on opposite ends of the parallelism spectrum. If we consider a send-receive code that sends two messages from a thread A to a thread B, in the most straightforward, synchronous case, parallelism is decreased by the imperative receive primitive:

#### Figure 2.6 Spectrum of parallelism

| // Thread 1                         | // Thread 2                         |  |  |

|-------------------------------------|-------------------------------------|--|--|

| <pre>send( 2, type1, data1 );</pre> | receive( type1, data1 );            |  |  |

| <pre>send( 2, type2, data2 );</pre> | <pre>receive( type2, data2 );</pre> |  |  |

Even if the semantics of the application may allow the messages to be processed in any order, the underlying model requires that the messages be received in the order sent, and the serial nature of code execution implies that one receive must precede the other. Though it is possible to express unordered reception via asynchronous send and receive primitives, such code is significantly more difficult to write. Thus, the basic MPI interface is represented at the left of the parallelism spectrum; the developer must apply more effort to express greater parallelism.

In the actor model, message reception may occur as long as the actor is not processing a prior message. In contrast to the MPI case above, the actor will receive whichever message arrives at the actor thread first. There is, however, a dual of the MPI case; if there is a dependence constraint on message processing, the actor must handle the case in which message reception order is reversed. In this case, the actor must delay processing of the second message until the first is received and processed. Thus, the actor model starts at the completely parallel end of the spectrum and requires that the programmer apply more effort to express less parallelism. The extreme amount of parallelism in an actor program can sometimes lead to difficulty in programming. To remedy this problem, most actor languages include constructs for shifting order maintenance from the programmer to the run time system. As will be seen in Chapter 3, combing the actor model with an imperative language such as C<sup>++</sup> also serves to simplify the expression of parallelism without putting an unacceptably large burden on the developer.

#### 2.3.4 Concurrency expression

There are a number of methods for expressing concurrency in wide use; among the most popular are data parallelism, task parallelism, and actor parallelism.

#### 2.3.4.1 Data parallelism

In data parallelism, parallelism is implicit in certain data structures, usually in arrays. Operations on arrays implicitly imply parallelism; it is the responsibility of the compiler and run time support to implement the parallelism. Data parallelism is most often applied to dense arrays but also may be applied to sparse data structures.

#### 2.3.4.2 Task parallelism

In task parallelism, parallelism is explicit, usually in the form of a parallel parfor or dowhile construct or an imperative spawn. In these cases, the body of the loop or the target of the spawn is performed concurrently with other parts of the computation. These types of parallel expression imply a degree of linkage between concurrency and the lexical structure of the program.

#### 2.3.4.3 Actor parallelism

In actor parallelism, the unit of concurrency is the actor, which is also the unit of interference control. Concurrency in an actor program is implicit in the semantics of the actor model. Interprocess communication is expressed via *continuation execution*, an extension of the member function execution mechanism of serial object-oriented languages. There are no imperative constructs for parallelization or synchronization similar to the parfor and barrier primitives typically found in task parallelism.

#### 2.3.5 Method of implementation

Pancake and Bergmark classify interfaces as concurrent languages, language extensions, and run time libraries [18].

#### 2.3.5.1 Languages

Language implementations provide the greatest flexibility but have the drawback of requiring more effort in development and maintenance of implementation, higher costs in training efforts, sacrifice of existing code, and inability to overcome inertia of existing usage. In the case of concurrent languages, a significant amount of effort can be required to specify the syntax and semantics of serial portions of the language, which detracts from the effort to address issues of concurrency.

#### 2.3.5.2 Language extensions

Language extensions mitigate, but do not eliminate, the difficulties of language implementations. An extension of an existing language represents less flexibility in expression but gains greater ability to utilize existing technologies in implementation. Training and adoption difficulties are fewer than in the language cases, but they are still significant.

#### 2.3.5.3 Libraries

Libraries provide the lowest startup costs, but they do so at the cost of least flexibility in expression and often the most effort in expressing parallelism. On the other hand, libraries provide the greatest ability to coexist with existing libraries and development tools.

## 2.4 Composability

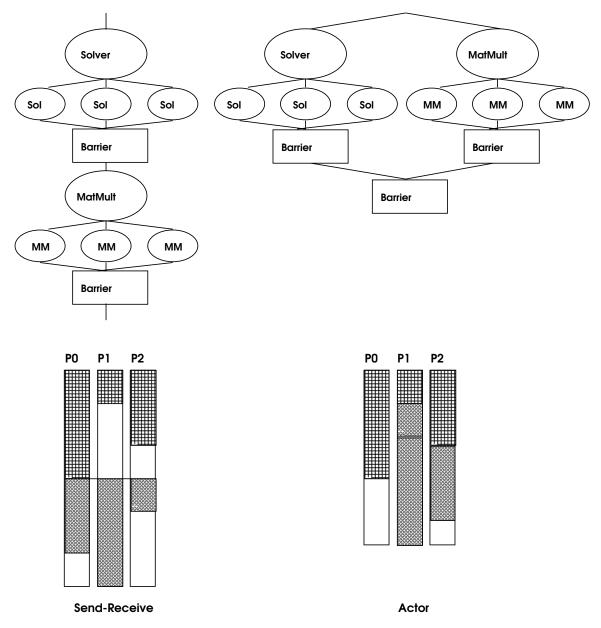

Of particular interest in this work is the ease of *composability*, the process of taking two existing modules for solving subproblems of a computation and combining them into a single application to solve a more complicated problem. For example, an application might require the use of a linear system solver and a matrix multiplication package. In this example, the implementation and component packages are composable if it is possible to take existing modules for the solver and multiplication tasks and use them, without modification, to solve the appropriate subproblems.

In composability, physical thread-based models tend to fall short of the virtual techniques because partitioning, usually static, of available processors is required. Designers of distributed memory interfaces such as MPI are implementing ways of solving this problem, but as yet there are few examples of such features.

Implementations of the actor model, being based on a virtual thread model, implicitly perform load balancing when a new actor is created. Thus, if an actor type exists for each of the solver and multiplication problems, an actor can be created for each problem without interfering with the other. It is the task of the run time system to load balance and schedule the actors to take advantage of available processing elements.

Figure 2.7 shows the difference between typical message passing and actor implementations of the linear system solver and matrix multiplication problems. In the message passing case, we assume that a procedure exists for each subproblem and that each procedure was designed assuming full use of the parallel machine. Each of the two subproblems is solved internally in parallel, but the two subproblems are sequentially ordered with barriers. In the

Figure 2.7 Composability in send-receive and actor models

actor case, since each subproblem is represented by an actor, the two actors, and by extension, the subproblem actors, are created concurrently and are synchronized only when the two operations are completed<sup>1</sup> which may result is higher processor efficiency.

<sup>&</sup>lt;sup>1</sup>The barriers shown in the actor example are abstract; though an actor model does not have blocking primitives, the sequence of continuation executions can effectively creates barriers.

# 2.5 A Class Library Approach

In this work, we present an interface and implementation for scalable concurrent objectoriented programming which is applicable to the irregular and unstructured problems of which VLSI CAD problems are representative. This section presents the major characteristics of the interface.

## 2.5.1 Scalability

The interface and implementation are applicable to a wide range of machines, from small shared memory workstations, through workstation clusters, to massively parallel processors (MPPs). By supporting small machines and workstation clusters as well as MPP architectures, we are able to facilitate near-term use on existing workstation clusters while at the same time enabling the exploration of the application of MPP architectures to CAD problems.

#### 2.5.2 Seamlessness

The interface is uniform across all supported architectures, from workstations to MPPs. This uniformity enables the exploration of concurrency using small machines and clusters while at the same time providing a continuous migration path to MPP machines. Development of CAD applications based on the environment allows experimentation across a wider range of architectures than has previously been possible.

#### 2.5.3 Multi-level abstraction

We have developed a multi-level abstraction based on two models. The high-level model, the actor interface, is capable of expressing actor operations that are easily implemented on virtually any machine, though at costs that will vary from architecture to architecture. The actor interface itself is implemented via a well-defined low-level model, the abstract parallel architecture, which captures details such as address space distribution while still unifying other architecture and vendor-specific details. Use of the actor interface does not preclude direct access to the abstract architecture interface. Furthermore, the actor interface has been carefully augmented to express several of the most common architecture-dependent features commonly used for data distribution.

#### 2.5.4 Medium-grain parallelism

Because the high-level actor interface augments the native C<sup>++</sup> interface, an application designed has the ability to express serial computation using only native C<sup>++</sup> constructs and parallel computation via the library interface.

#### 2.5.5 Class library interface and implementation

The interface, implemented as a library in the C<sup>++</sup> programming language, enables the continued use of existing development tools, e.g., compilers and debuggers. The use of the C<sup>++</sup> language enables migration from existing C and C<sup>++</sup> codes that predominate in VLSI CAD. The library approach has had the added benefit of forcing a tighter integration with the serial language, a goal which is decidedly difficult to attain [18]. It also facilitates incremental parallelism in two ways. First, the library approach described implies that a serial program with no calls to the library is a degenerate library client. Incrementally greater parallelism is expressed by adding additional library primitives. Second, we implement parallelism via derivation; in a very real sense, the parallel application is *derived* from the serial application. By applying parallelism via derivation—the dynamic-binding mechanism in C<sup>++</sup>—it is possible to share object code and to limit perturbation of the original serial code.

# 2.6 Other Models and Implementations

In this section, we survey and briefly compare the approaches represented in this work to nonactor models and implementations. Other actor approaches are considered in Section 3.6.

#### 2.6.1 pC++

Gannon and Lee [21], [22], [23], [24] have developed pC++, an extension of C++ with support for distributed data structures similar to FORTRAN D. The pC++ language provides support for distributed collections, both array-based and tree-based, of arbitrary types and with full support for the C++ mechanisms of derivation and dynamic-binding [21]. In their data parallel model, a data structure, usually an array, is distributed across processors in a regular manner. This type of expression is natural in scientific computing where many algorithms are described as operations on arrays. It is difficult to hypothesize how one would implement the unstructured applications in VLSI CAD on top of a data parallel model. The

difficulty of expressing these tasks in terms of data parallelism reinforces the necessity to choose the correct tool for the correct problem.

#### 2.6.2 CC++

Compositional C<sup>++</sup>, or CC<sup>++</sup>, proposed by Chandy and Kesselman [25] takes a task parallelism approach to concurrency. Where in pC<sup>++</sup>, processor control is implicit in the parallel data structures, in CC<sup>++</sup>, parallelism is achieved though par and parfor primitives which cause code blocks to be performed concurrently in different processing threads. CC<sup>++</sup> also provides a number of synchronization primitives necessary for a thread-oriented programming interface.

To express VLSI CAD applications in terms of task parallelism, applications are broken into a number of similarly sized tasks. The greatest difficulty in applying this technique is the necessity to guide the ordering of task execution; often parallel CAD algorithms are sensitive to ordering of execution. Task parallelism generally does not provide a priority mechanism. Furthermore, many task parallelism implementations are tuned for cases where the degree of parallelism expressed is on the order of the number of threads in the machine. In this situation, a master-slave model would often be required to maintain an ordered list of tasks. This lightweight scheduling is implicit in the actor interface.

As is the case for data parallelism, there are problems for which task parallelism and CC<sup>++</sup> more closely match the most intuitive solution. In particular, while features such as implicit barriers and futures can be expressed with continuations, such expression may be cumbersome. Applications that rely heavily on these operations could be tedious to translate to continuation passing style.

#### 2.6.3 IC-C++

Recently, a variant of C<sup>++</sup>, Illinois Concert C<sup>++</sup> or IC-C<sup>++</sup>, has been proposed as a method for the expression of fine-grain concurrency in C<sup>++</sup> [26]. IC-C<sup>++</sup> is targeted at massively parallel machines and applications with a high degree of concurrency. IC-C<sup>++</sup> defines a concurrent semantics for most C<sup>++</sup> primitives and operations, which enables the easy expression of a high degree of concurrency. The work on IC-C<sup>++</sup> borrows from the compiler analysis technologies in the Concert system [27].

#### 2.6.4 ES-Kit

The Experimental Systems Kernel, or ES-kit, of Leddy and Smith [28] is implemented via modifications to an existing C<sup>++</sup> compiler and as such tries to stay true to the spirit and syntax of C<sup>++</sup>. In ES-kit, pointers are extended to represent a global namespace, and remote execution is represented by the execution of a method call though a pointer to a nonlocal address. Object distribution is either automatic or under program control via the C<sup>++</sup> placement syntax [29]. Parallelism in ES-kit is specified through the use of remote function calls and futures [30]. The original target of the ES-Kit was special purpose hardware.

#### 2.6.5 Amber

The Amber system [31], derived from Presto [32], is an extension of C<sup>++</sup>, via a preprocessor and a supporting run time library, targeted specifically toward workstation clusters running the Topaz operating system [33]. In Amber, the approach is to explicitly locate a shared datum on a particular node and then to cluster Topaz threads on that node. When access is made to a remote node, the run time system traps to the Amber kernel and the thread of control is transferred to the processor on which the data value resides.

#### 2.6.6 COOL

COOL, developed by Chandra, Gupta, and Hennessy [34], is also based on thread-explicit extensions to C<sup>++</sup>, in this case targeted toward shared memory architectures in general and toward the DASH architecture in particular. COOL provides a full range of classical synchronization constructs. Of particular interest in COOL is the ability to represent the affinity of different objects, which is necessary to achieve high processor utilization in DASH's distributed shared memory architecture.

#### 2.6.7 Linda

Linda, developed by Carriero and Gelernter [35], [36], represents a high-level approach to concurrent processing. In Linda, shared data are represented by a shared *tuple-space* to which all functions have access. Elements in the tuple-space are lists of values. Access to the space is via pattern matching on one or more elements of a tuple. This formulation has particular benefit in logic-programming and artificial intelligence and was one of the motivations for the development of ActorSpaces [37], [38], an extension to the actor model.

Linda has been applied to coarse-grain VLSI applications [39] and implemented on a number of architectures [39], [40], including an implementation that runs atop PVM [14] and thus runs on any cluster of machines supported by PVM [41].

Linda was specifically designed as a *coordination language* to be added to a *computation language* [35], which is both an advantage and a disadvantage. While it allows easy separation of control flow from data flow, this separation violates the object model and thus limits application in object-oriented environments.

#### 2.6.8 Concurrent C++

Concurrent C<sup>++</sup>, developed by Gehani and Roome [42], [43], is another extension of C<sup>++</sup>. In Concurrent C<sup>++</sup>, processes communicate via transactions that can be either blocking or nonblocking. Process bodies in Concurrent C<sup>++</sup> are represented by functions, generally with an infinite loop representing the way the process handles events. Concurrent C<sup>++</sup> has been implemented on uniprocessors, workstation clusters, and shared memory multiprocessors [43].

#### 2.6.9 Jade

Jade is a high-level language for coarse-grain concurrency [44]. Jade uses a single address space model for communication with explicit declaration of data dependencies; the overall model is one of task parallelism. Jade has been implemented as an extension of the C programming language on shared and distributed memory machines and on heterogeneous workstation clusters.

#### 2.6.10 Mentat

Mentat, developed at the University of Virginia [45], [46], is an environment for coarsegrain parallel application development. The Mentat language is derived from C<sup>++</sup> and includes support for explicitly identified parallel class types. One of the more interesting aspects of Mentat is the run time tracking and enforcement of data dependencies. The coarsegrain nature of Mentat stems from the fact that all active classes in Mentat have separate address spaces; the operating system overhead required to implement separate address spaces generally precludes a large number of objects.

#### **2.6.11** μ**C++**

Buhr et al. [47] developed  $\mu C^{++}$  by adding four classical concurrency abstractions to C<sup>++</sup>: coroutines, monitors, coroutine-monitor, and task. The communication model in  $\mu C^{++}$  is a single address space, and implementations support only shared memory multiprocessors. Threads are represented in  $\mu C^{++}$  by special, explicitly declared coroutine class types. In addition to mutex and other synchronization types,  $\mu C^{++}$  allows for conditional acceptance of communication, all of which occurs via member function calls. Thread context switches in the current  $\mu C^{++}$  implementation occur at the user level without the necessity for operating system calls.

#### 2.6.12 Paragon

The Paragon project of Chase, Cheung, Reeves and Smith [48] is implemented via a C<sup>++</sup> library for the support of distributed data structures. Support is provided for distributed arrays, both through partitioning and replication. Paragon also provides permutation and reduction operators as well as a number of interesting conditional structures for expressing spatial and temporal distribution.

#### 2.6.13 CA/C++